Thanks to a complete filtration we have been able to see in detail the complete line of EPYC Genoa processors that AMD should launch at the end of this year, and that it will be based on the Zen 4 architecture. As many of our readers will remember, this architecture will bring important changes, among which we can highlight the increase of the L2 cache to 1 MB per core and an approximate 15% improvement in single-wire performance.

Another novelty that will be fundamental in the Zen 4 architecture is the jump to TSMC’s 5nm node. This new manufacturing process will reduce the size of the transistors, allowing AMD to significantly increase the maximum number of cores and threads in the new EPYC Genoa processors. For comparison purposes, it is enough to remember that the most powerful chip within the current generation, based on Zen 3 and manufactured in 7nm, has 64 cores and 128 threads, while the top of the range of the EPYC Genoa series will come with 96 cores and 192 threads.

AMD has also highlighted other interesting developments, such as support for DDR5 memory and the new PCIe Gen5 standard, and we must not use a new socket, the SP5 (LGA-6096). This new socket will allow the maximum TDP to be increased, going from the 450 watts of SP3 to a maximum of 700 watts. Obviously, this is necessary for that large increase in cores to be viable, since we are talking about a 50% increase.

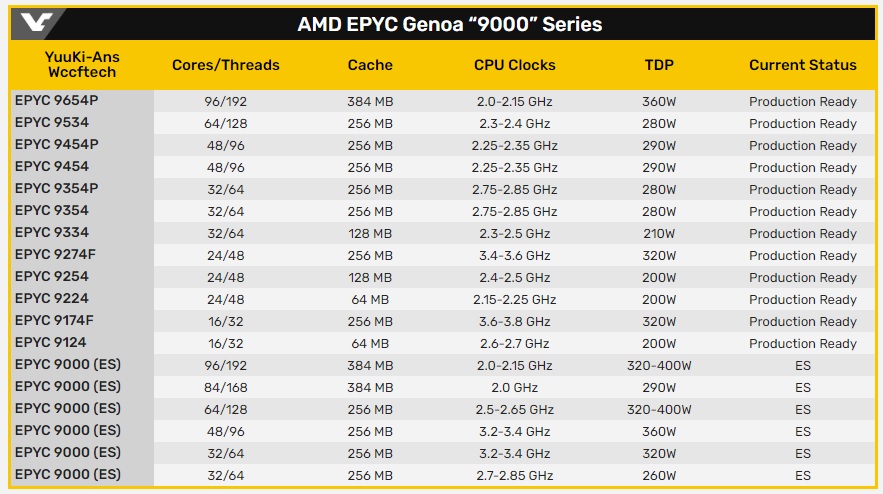

As we can see in the attached table. in total AMD will release a total of 18 EPYC Genoa processors, which will use the “9000” nomenclature and come in configurations ranging from 16 cores and 32 threads to the aforementioned 96 cores and 128 threads. In intermediate positions will be the classic configurations of 24 cores and 48 threads, 32 cores and 64 threads, 48 cores and 96 threads and 64 cores and 128 threads. We can also see a model listed with a configuration of 84 cores and 168 threads, which will become the second most powerful chip of this new generation.

On the right side we can see the amount of L3 cache that each processor will have, the working frequencies, the TDP and the state in which it is. Most are ready for manufacturing, while the acronym “ES” refers to the fact that AMD already has functional engineering samples of these processors. Please note that the working frequencies refer to the base values, and that the maximum values in turbo mode should be much higher.