It has been the R&D department of Kioxia (formerly known as Toshiba Memory) who have shared their findings and research regarding memory 6-bit NAND Flash per cell, a set goal that will allow memory density to scale to unprecedented levels and could potentially become the future of storage in the medium term as long as these findings are brought to fruition.

6-bit memory per cell … but with liquid nitrogen

The advances in NAND Flash memory are oriented, as is logical, towards achieving a higher density and for this they must be able to store a greater amount of bits per cell. Now the Kioxia researchers have shown that it is possible to get a working 6-bit memory cell, but with a few cooling requirements which obviously don’t make it viable for the consumer market, at least for now.

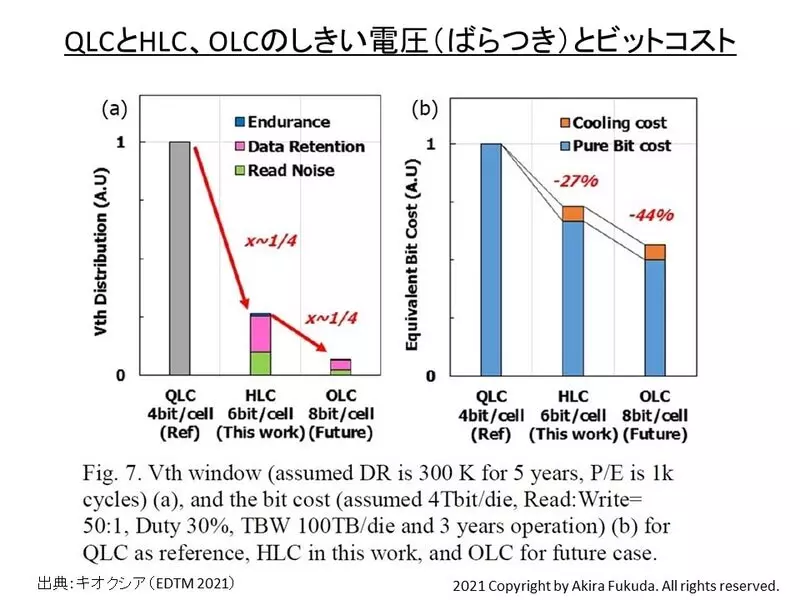

The number of necessary states is doubled with each bit: in SLC NAND memory with 1 bit it is 2 states, with 2-bit MLC it is 4 states, with 3-bit TLC it is 8 states and with 4-bit QLC per cell there are 16 states (with PLC of 5 bits per cell the states are 32, although this technology is not yet commercial), so the HLC-NAND memory would have 64 states. The more states to differentiate, the more complex and slower the programming or writing in the memory cell, so the performance and the durability decrease at the same rate as the increase in density.

Therefore, performance and durability are similarly decreased while the requirements for error correction are increased; mapping the 6-bit information requires 64 voltage states within each cell as explained earlier, and this for now also causes an operating temperature that requires extreme cooling to be possible.

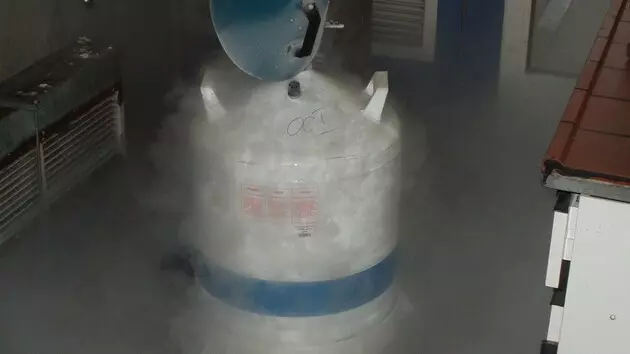

To achieve 64 voltage states with current 3D NAND technology, the chip had to be immersed in liquid nitrogen at 196 ° C below zero, something necessary to reduce voltage fluctuations (so-called signal noise) as well as the loss of electrons from emission. thermionics. The durability of the HLC cell is said to have been increased from 100 to 1,000 read cycles with this method, which roughly corresponds to the level of 4-bit QLC cells which, however, do not require this extreme cooling.

5-bit PLC memory will come first

Before the 6 bits per cell HLC-NAND memory arrives, the previous step has to arrive first, the memory Penta Level Cell (PLC) with 5 bits per memory cell. In this area also Kioxia is investigating a practical solution together with its partner Western Digital, and two years ago they already spoke about it in a conference during the Flash Memory Summit 2019. A few months later, Kioxia presented «Twin BiCS Flash«, A new type of structure that should allow more than 4 bits per cell, including PLC.

At the moment this solution seems to be still far from being available; Western Digital CTO Siva Sivaram said in June that he does not expect PLC memory to hit the market until the second half of the current decade (that is, until at least 2026), and therefore if we are still far from the PLC memory, imagine the 6-bit HLC.

In any case, manufacturers for now are focusing on offering more layers stacked on top of one another in what is known as 3D NAND to increase memory density and reduce wafer costs. Today the industry has already managed to reach 176 layers in functional memory chips, and manufacturers like Samsung are already tinkering with more than 200 layers, while stating that they have set a goal of reaching 1,000 layers.