There is no doubt that Zen 4 is going to be a very big change in performance by AMD, all supported by the adoption of TSMC’s 5 nm node for the design and construction of a much more complex CPU that allows to achieve a higher CPI than its predecessors.

One of the key points to achieve higher performance is the design of the cache, not only how fast it is, but also the amount of information it can hold and the simultaneous accesses it supports. A higher number of instructions resolved per cycle also results in a higher number of accesses and in an increase in the size of the same.

Zen 4 Cores L2 Cache Changes

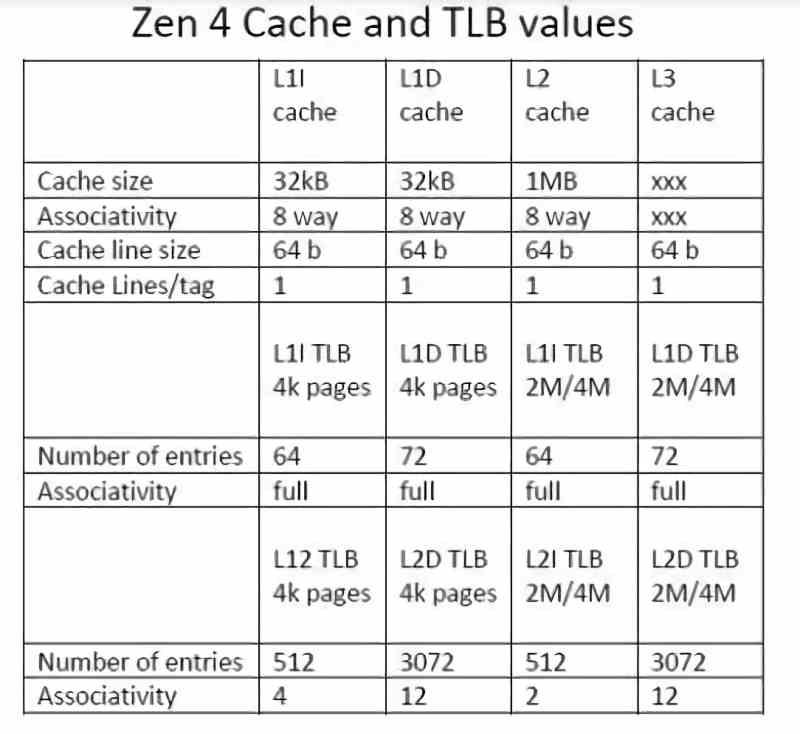

Through a series of leaks, details of the next generation of AMD CPUs have been known in advance. This time it was the L2 cache of Zen 4, which, as you can see in the table above, would have gone from 0.5 MB or 512 KB per core to 1MB, thus doubling its capacity.

In Zen architectures, the L2 cache is private for each of the cores, with L3 being used as LLC for each group. From the information that has been leaking we know that Zen 4 will continue with the 8-core configuration around the L3, each with its corresponding L1 and L2 caches, so doubling the size of the L2 cache on the new CPUs serves to improve the CPI by increasing the chances that the necessary data and instructions do not have to go to L3, and therefore any hit at that level is resolved much earlier.

AMD has a great challenge ahead

Well, really little, although we have to assume that its increase in the IPC is going to be much higher than the 15% granted by the version with V-Cache of Zen 3+. The data being shuffled speaks of an increase in the CPI of 19%, which would be too low a jump if we take into account the improved iteration of its predecessor. In any case, the completion of the design of the Zen 4 cores could not have been completed and the team led by Mike Clark still has time to improve, what’s more, we believe that the launch of the improved Zen 3 (Zen 3+ supposedly) It is a way to give time to the completion of Zen 4.

At the moment AMD has not filtered the amount of L3 that Zen 4 will have, this makes us think that they are considering launching the fourth generation Zen with vertical cache from the first moment, which would mean a performance improvement over the original design . The trade-off is that this will make production more expensive. Is that why AMD will launch its Zen 3 with V-Cache with the intention of testing the market?

With an Intel that has put the batteries with Alder Lake-S and that has already finished the design of Meteor Lake for 2023, it is up to AMD to make Zen 4 as competitive as possible. They have to be more ambitious than with Zen 3 where they were limited to TSMC’s 7nm node.