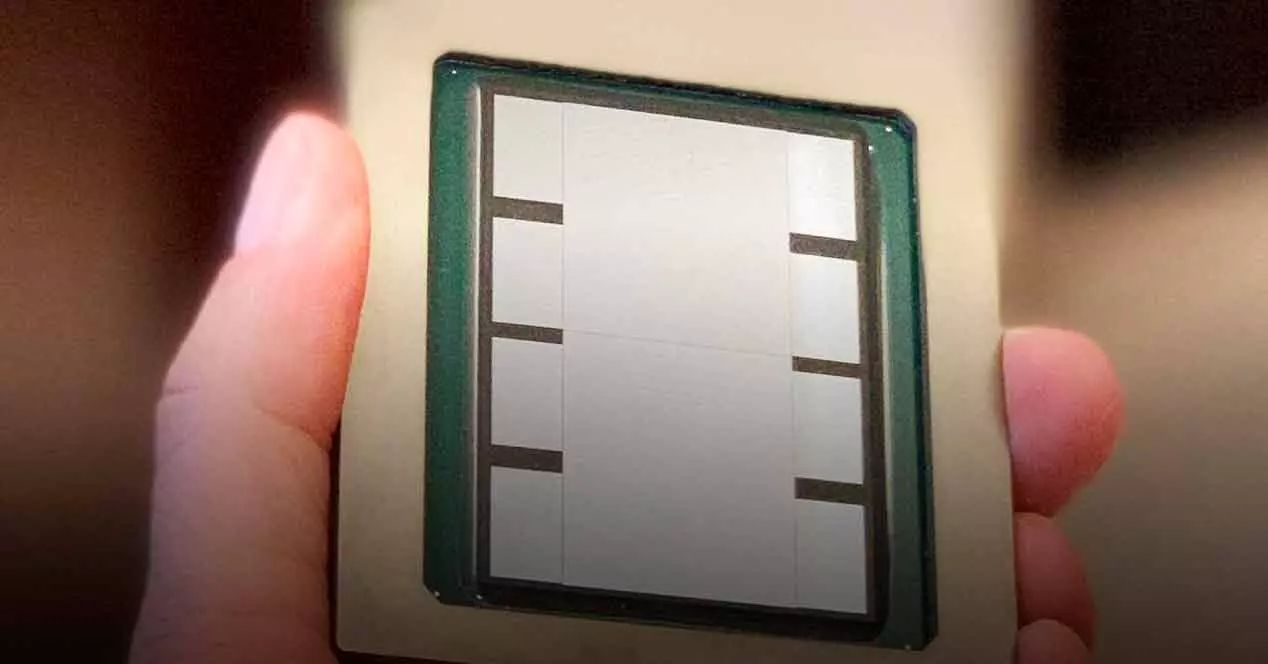

TSMC’s 2.5DIC packaging technology has undergone a major advance in recent months, specifically with the launch of the fifth generation of CoWoS-S. Which allows integrating processors with HBM interfaces of up to 8192 bits and therefore up to 8 HBM 2 stacks in the interposer. The first to release the new packaging? AMD with its Dual GPU for high performance computing Aldebaran or better known as AMD Instint MI200.

TSMC tells us about the past, present and future CoWoS-S in the Hot Chips

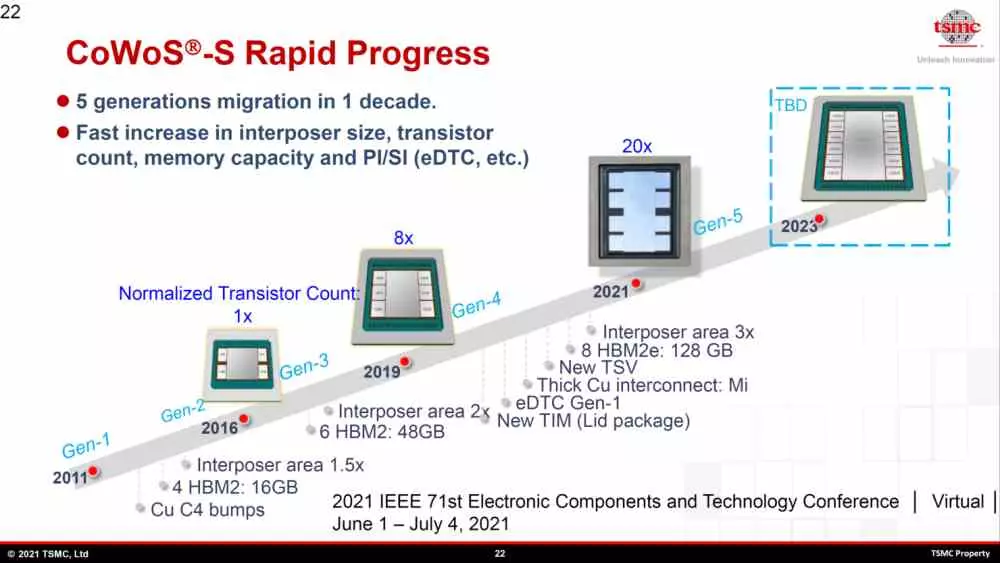

TSMC has been developing its 2.5DIC CoWoS packaging technology for over a decade, which comes in two versions. On the one hand, CoWoS-S that makes use of a silicon interposer. On the other, CoWoS-R and CoWoS-L uses a silicon bridge for intercommunication. At a commercial level, CoWoS-S was launched from the third generation, which was launched in 2016 with the launch of the first high-end GPUs with HBM memory, which were based on the AMD Fury and NVIDIA Pascal architecture.

The so-called fifth generation brings an interposer that is three times larger than five years ago and 2.5 times larger than the fourth generation. Which is used by the NVIDIA A100 GPU. This increase has allowed that from 2016 to 2021 we have seen a 20-fold increase in the number of transistors in total, an increase well above the traditional one by Moore’s Law, but which has been based on having increasingly complex structures. They have achieved this by implementing a new type of interconnection called Thick Cu Interconnect.

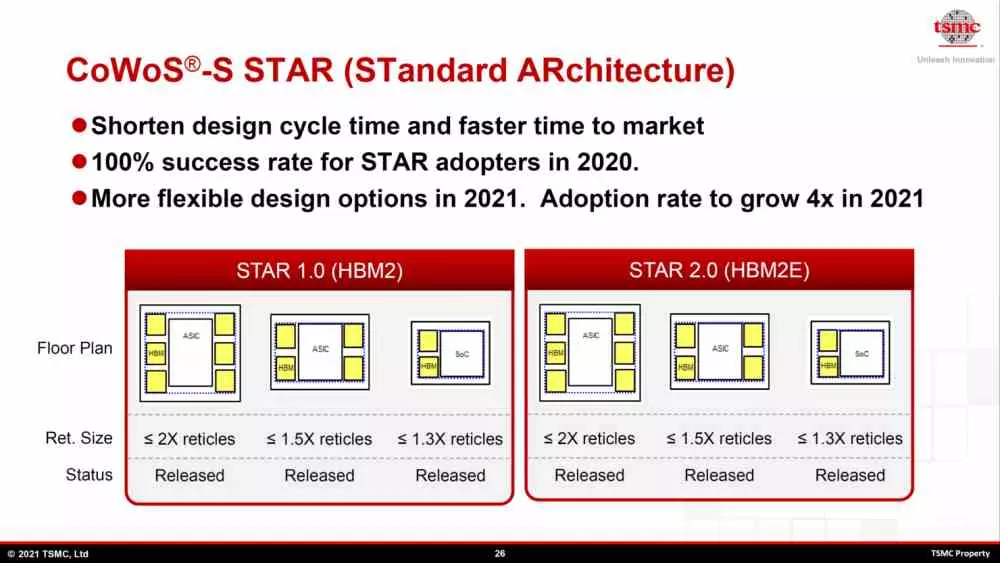

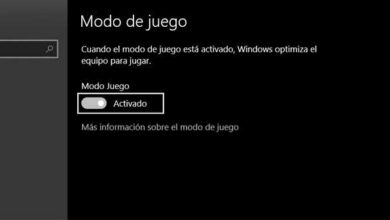

Another novelty has to do with the introduction time of CoWoS-based designs to the market, which is why they have designed a semi-custom solution for chip design under the name of CoWoS-S STAR. Being a semi-custom design this allows most chip designers not to have to create their own design and can license TSMC’s. This not only allows them to advance the time of deployment to the market, but also increases the number of companies that can make use of this technology. TSMC expects the number of its clients to use CoWoS-S STAR to quadruple.

TSMC prepares to compete against Intel in 3DIC and 2.5DIC

We know that Intel is going to combine its EMIB and Foveros technologies in extremely complex packages, the proof of which is Ponte Vecchio that brings together several of these technologies. Since TSMC is its main rival and Intel intends to rent its factories to third parties, they cannot be left behind and the future is to combine CoWOS technologies of different types with SoIC technology. Being CoWoS the equivalent to Intel EMIB and SoIC to Foveros.

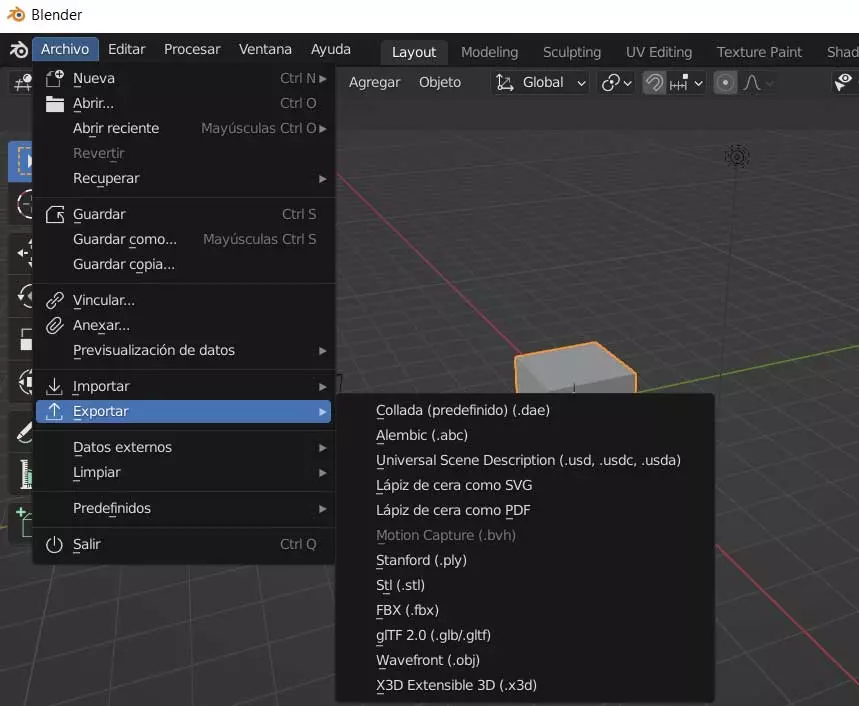

At the moment we know little about the sixth generation of CoWoS-S, but it is expected that the number of HBM chips will increase again, as well as the size of the Interposer, but we will also see the union of SoIC technologies, either in their variants WoW or CoW. We also know that TSMC is preparing for the implementation of HBM3 memory, the standard of which is not finished. In any case TSMC tells us about a launch for 2023. Will this be the date of the NVIDIA Hopper GPU? We do not know, but it seems that the next in HPC GPUs we will not see until 2023. At the moment in the fifth generation of the NVIDIA CoWoS-S technology it is the great absent.