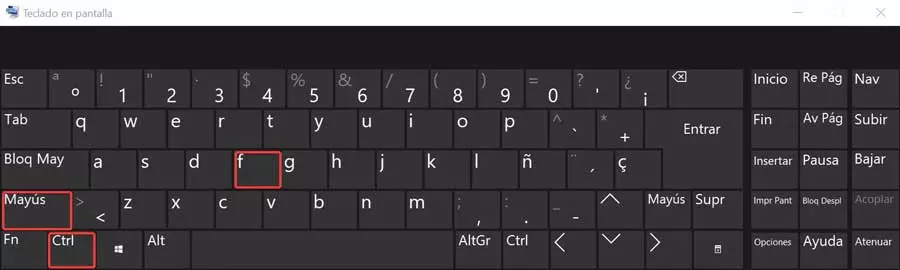

In order for our readers to understand the importance of AMD’s change in the integrated memory controller of its Zen 4, we have to clarify a basic concept. Access to RAM is not continuous, but the signal is synchronized in a process of different periods in which the signal between both components, the memory and the processor, are synchronized. Something that we explain in detail in an article about how a processor and its RAM communicate.

So when we talk about access latency we are not talking about communication speed understood as the amount of data that is transmitted in a unit of time. That is the bandwidth and this is given in an unrealistic way, because there are access windows that prevent communication from being given 100% of the time. The paradox of DDR5 compared to DDR4 is that although it is much faster, it has a higher latency, measured in cycles. Does that mean it’s slower? No, due to the fact that DDR5 transmits more data in the same amount of time than DDR4, however, there is a special case

The new DDR5 memory controller for AMD Zen 4

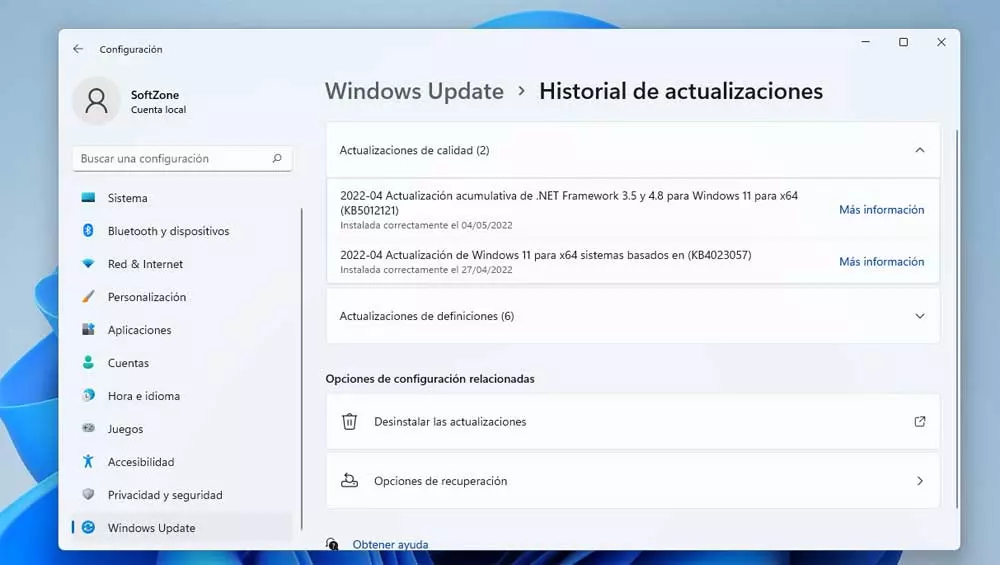

AMD will abandon the use of DDR4 memory in its Ryzen 7000 based on Zen 4 architecture, this means a new memory controller compatible with DDR5 that is expected to be able to reach a transfer speed of 5.2 billion transfers per second. For other faster memories, the controller would use the classic method of dividing its clock speed in half, as long as it does not exceed the power consumption limit of that part of the processor and that the signal is synchronized.

Its biggest novelty? The ability to lower clock speed to memory and BMI in exchange for reducing access latency time. This, which may seem counterproductive, is key in certain scenarios where latency is more important than bandwidth. So when it comes to operating with DDR5, Zen 4 will start from two different dynamic profiles. One for latency-sensitive applications and one for those requiring bandwidth.

The key is that the more bandwidth you have with memory, the greater the number of requests made to RAM, so reducing bandwidth also reduces the number of requests to RAM. Decreasing the workload of the IMC and consequently decreasing latency.

Other optimizations we expect in the Ryzen 7000

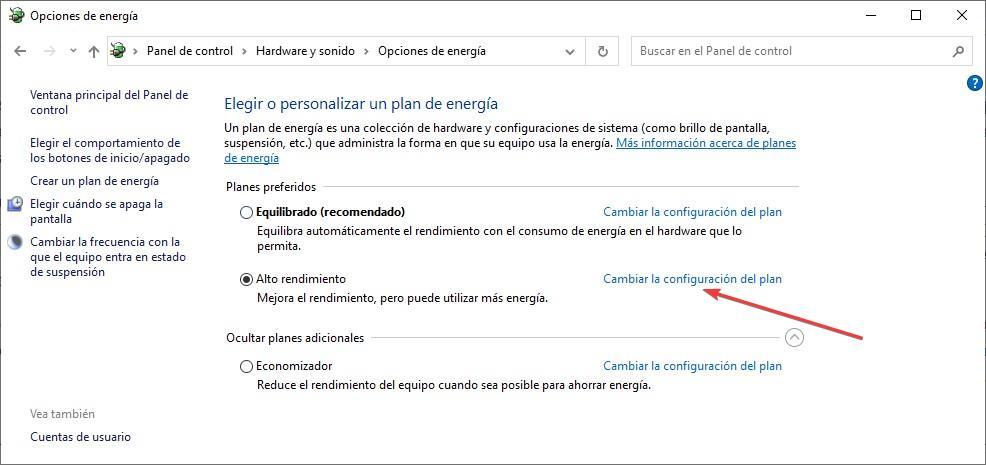

There are two key performance improvements in the Ryzen 7000 that we expect AMD to have implemented in its next generation of processors. The first of these is the decrease in access cycles to the different cache levels, something in which Intel has had a wide advantage in the latest generations of processors and one of the weak points to be solved by Lisa Su .

The latency increase from DDR5 widens the distance between the processor and memory even more, so there is some scope for future processors to have a new level of cache or to adopt V-Cache, which has something to do with it. more latency, but it increases the time of hits in the cache. In any case, for the Zen 4 with V-Cache we will still have to wait and we are very clear that AMD will implement the second generation, with a much higher capacity.