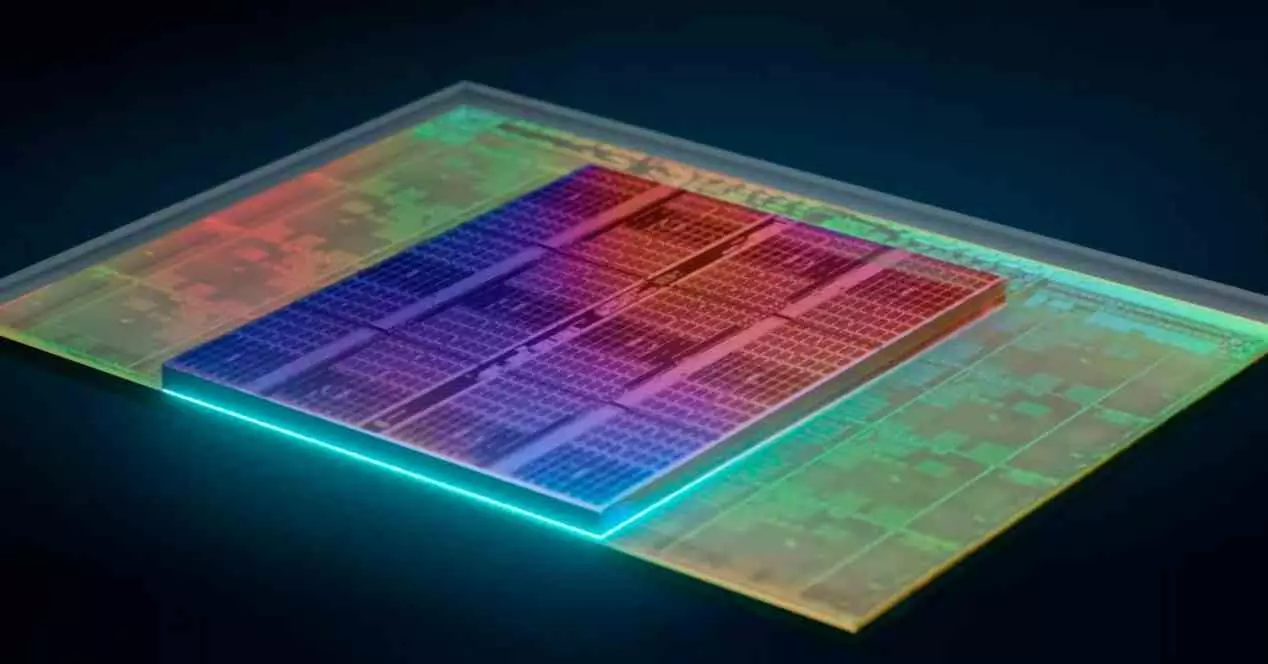

The vertical cache was one of the great architectural novelties that AMD presented last year and that it has introduced in its Ryzen 5800X3D CPUs for desktops and Milan-X for servers. However, until now it was unknown in many points such as communication with the processor. Well, they have given new details of the operation of the V-Cache at the ISSCC 2022, let’s see what they are.

As the chasm between processors and memory widens, architects of new processors need to find a way to prevent this from becoming a performance bottleneck. AMD’s solution? Increase the L3 cache of your Zen 3 processors, but in such a way that the size of the processor does not increase. How? By creating a separate chip, stacking it on top of the processor, and developing a communication system to vertically intercommunicate the two that is fast enough to function as a cache. The objective of this is easy, the performance of an instruction depends on how long it takes to find the data and it will find it before in the cache rather than in main memory. Unfortunately, memory space within a processor is limited.

New AMD V-Cache details at ISSCC 2022

Taking advantage of the celebration of the already classic conference on hardware architectures in which the different companies talk about their achievements and milestones in the past year. AMD has taken advantage of the ISSCC event in 2022 to give new details of its V-Cache. Which we did not know until now and refer to the way in which the SRAM communicates vertically with the CCD Chiplet Zen 3, but before that we have to review the communication topology,

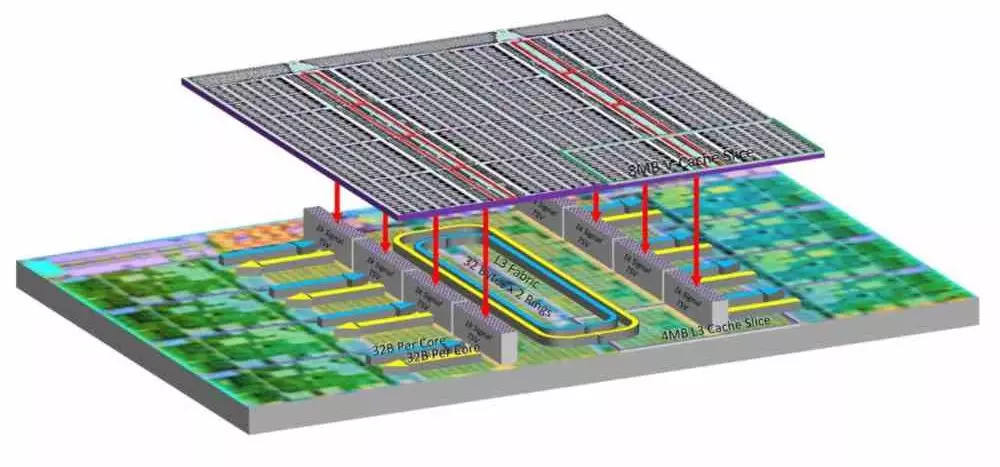

While a CCD Chiplet in Zen 2 makes use of a crossbar to intercommunicate the 4 cores with each other, the increase to 8 cores in Zen 3 forced AMD to make use of a ring topology for the communication between the different cores with each other and with the last level shared cache, which is the third level.

Well, to communicate with the V Cacheeach core has a total of 1024 pins vertical doing use of TSV intercomsthis means that for each cycle, 8192 bit with a total bandwidth of 2TB/s in Full Duplex mode and therefore in both directions at the same time. Which means that the clock speed of the communication interface is 0.977GHz. All this through a copper link where soldering is not necessary.

New SRAM cells used

As for the type of SRAM used in the V-Cache, it is different from the one used in the CCD Chiplet. Since AMD for the SRAM in the V-Cache makes use of high-density (HD) memory cells) instead of the high current (HC) bit cells. This results in energy savings per data transfer from the 14% and it is a 24% in terms of size versus capacity.

Beyond Zen 3D

The V-Cache presentation at ISSCC 2022 made one thing very clear: we are going to see a version of Zen 4 with V-Cache. Although it has not been officially announced, we do know that the internal communication topology will be the same as its predecessor and, therefore, there will be no problem creating a version with vertical cache.

Speaking of darker things, the Infinity Cache in RDNA 3 is rumored to go on a separate chip alongside the memory controller in the form of stacked memory, which matches the description of what the V-Cache is. At least if we pay attention to the patents of AMD itself. Now that we know that V-Cache has an interface that scales with the number of clients, we now know how it can scale in complex systems.