One of the challenges of three-dimensional integrated circuits or 3DICs is in the type of interconnections used to vertically connect the different logic and / or memory chips to each other. The best known method is the TSV, but the complications and extra cost in its manufacture have led different foundries to end up developing alternative solutions, all of them based on the so-called silicon bridges for interconnection. Until now we were familiar with Intel’s EMIB technology and AMD’s X3D, the latter in collaboration with TSMC.

The latest to join has been IBM, which has developed a silicon bridge that promises to lower the production costs of future 3DIC designs, which they have dubbed DBHi.

Intel simplifies silicon bridges with DBHi technology

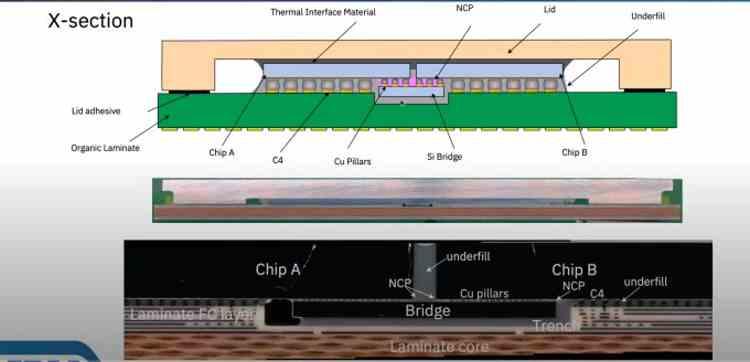

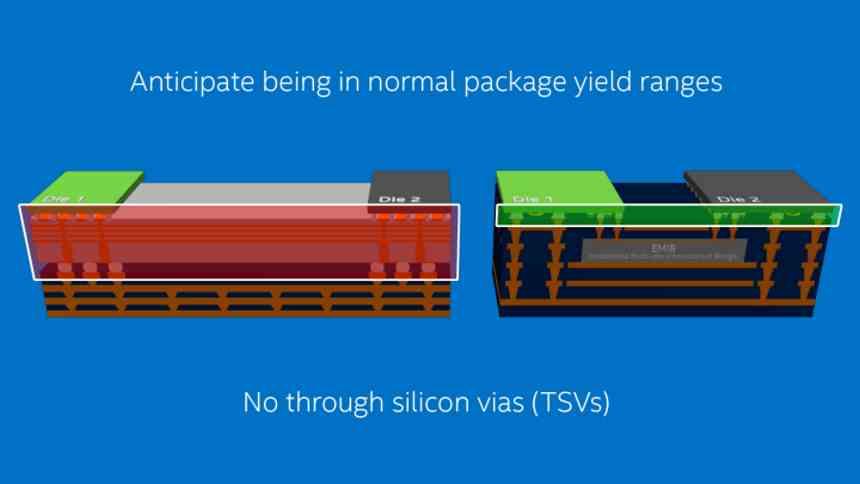

IBM has long stopped manufacturing chips, but it has not stopped investigating the development of new technologies, such as the development of a 2 nm node and now They surprise us with the development of their silicon bridge, which they have named DBHi, acronyms that stand for direct bonded heterogenous integration. Which consists of a silicon bridge to interconnect two chips vertically, without the need for TSV interconnections, which is located between the layers of vertically manufactured processors, for future CPUs, GPUs and APUs in 3DIC and 2.5DIC models.

The main difference between this and Intel EMIB technology is that the chips are bonded to the laminate with standard C4 bumps and the bridge connects the chips or chiplets with micro bumps formed on each side of the silicon bridge. A design that is simpler than Intel’s and therefore easier to manufacture than this. We do not know at the moment if any foundry is going to adopt this technology for future 2.5DIC and 3DIC configurations, since Intel and TSMC, the two largest have their own developed solutions.

The emergence of chips with 3DIC and 2.5DIC configurations has been seen as the solution to many of the problems of Moore’s Law when it comes to scaling chip performance in the future. Its non-adoption has been due to the high cost of manufacturing this type of integrated circuits using silicon pathways. Which has forced research and development in this field by large foundries.

The future passes through silicon bridges

The bandwidth required to interconnect future chips requires vertical interconnections, as this allows increasing the number of interconnections. The advantage of this is that it allows the energy consumption for intercom to be reduced to tolerable levels. Something that would be totally achievable with classic serial connectivity.

We have cases like Intel Foveros and EMIB, as well as future X3D technology from AMD. Which will be used for future processors for servers and data centers. However, we cannot also forget the development of new server processors based on architectures such as ARM and RISC-V, where IBM’s development of licensing is going to give them a great push towards much more advanced designs.